半導体においては、FEOL(Front End of Line)で作られたトランジスタなどの素子を、BEOL(Back End of Line)で配線形成することで、最終的にチップとしての機能が実現されます。

本記事では微細化に伴って従来のアルミニウム(Al)配線の課題と、これに変わる銅(Cu)/ 低誘電率(Low-k)材料による配線技術についてまとめます。

Al配線の限界

微細化が進む中で、トランジスタ同士をつなぐ配線もこれに合わせて最適化しなければ、チップ全体の性能が制約を受けます。Al配線では、以下の3点が大きな課題となりました。

- 配線遅延:配線の抵抗(R)と絶縁膜の静電容量(C)によって信号伝達が遅延。

- エレクトロマイグレーション:金属原子が移動し、配線が断線・ショート。

- 界面反応:AlがSiO2と反応し、絶縁破壊を引き起こす。

これらは、配線の材料・構造・製造方法など多方面に関わる課題です。

配線遅延と材料選定の進化

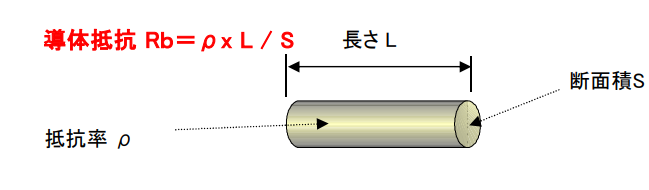

配線遅延とは、金属配線の抵抗(R)と、隣接する配線との間にある絶縁膜の静電容量(C)によって生じる信号伝搬の遅れです。

ここで静電容量とは、電極間に蓄えられる電荷の大きさを示す指標であり、導体間の電気的な影響の受けやすさを示します。

これらの積(RC時定数)が大きくなると、信号の立ち上がりが遅くなり、回路を高速に動作させることが難しくなります。

微細化が進むと、配線が細く長くなり電気抵抗(R)が増加します。

さらに絶縁膜(SiO2)が薄くなると、電極間の距離(d)が小さくなり、静電容量(C)が増加します。そのために配線遅延が無視できない問題になります。

これに加え、クロストーク(信号の干渉)も増加し、回路全体の信頼性(意図通りの電気的性能を長期間維持できるか)が損なわれます。

エレクトロマイグレーションとは

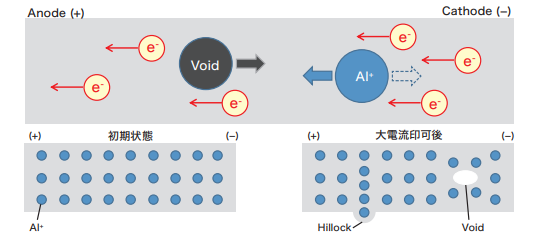

エレクトロマイグレーション(EM:electromigration)は、金属中を流れる電子の運動量が金属原子に伝達されることで、原子が徐々に移動してしまう現象です。これは、通常の格子振動によるジュール加熱(電流による加熱)とは異なり、高電流密度・高温下で特に顕著に表れます。

電子は外部電圧によりに押されて移動するため、金属原子は電子の流れる方向に押し出されます。この原子の移動によって以下の現象が生じます。

カソード側(ー側)

- 原子が失われて空隙(void)が生成、

- 配線の断線を引き起こす原因となります。

アノード側(+側)

- 原子が集積してヒロック(hillock)と呼ばれる突起が形成、

- 突起が膜厚方向に成長し、隣接層とショートを引き起こすおそれがあります。

※エレクトロマイグレーションにおいては、配線の電源接続を基準として、電子はカソード(ー)からアノード(+)へ流れます。このとき、金属原子は電子の流れる方向(カソード⇒アノード)へと押し流されます。

微細化との関係

半導体デバイスの微細化が進むと、結晶粒径が小さくなり、粒界(結晶粒の境界)の比率が増加し、粒界は原子の移動経路となりやすいため、さらにEMの進行が加速されます。

SiO2との界面反応

Alは融点も低く(660℃)、加熱されると容易に他の材料と反応しやすくなり、熱的・化学的に活性であるという特徴があります。この特性により、半導体製造プロセスにおいてはさまざまな材料との反応が問題になります。

SiO₂との反応メカニズム

特に、SiO₂膜とは高温環境下で反応しやすく、以下の酸化還元反応を起こします。

2Al + (3/2)SiO2 → Al2O3 + (3/2)Siこの反応では、Alが酸化されてAl₂O₃(酸化アルミニウム)になり、SiO₂が還元されて遊離Siになります。

問題の発生

この反応によって生成されたSiが、本来絶縁膜であるはずのSiO₂層の内部に存在することとなります。Siは導電性を持つため、絶縁膜の絶縁性が損なわれ、リーク電流発生、デバイス性能の劣化といった結果を引き起こします。

解決策:バリア層の導入

そこで、バリア層(例:Ti/TiNなど)をAlとSiO₂との間に挿入し、直接の反応を防ぐ必要がありました。

バリア層は、AlとSiO₂の直接接触を阻止する拡散防止機能を有し、両材料との密着性を提供します。

Low-k材料の採用

配線遅延の観点から

微細化が進む中で、配線間の静電容量金属配線の抵抗(R)と絶縁膜の静電容量(C)が増加し、これらの積(RC時定数)が大きくな配線遅延がチップ性能のボトルネックとなってきました。

これを解消するため、配線抵抗と絶縁膜の静電容量の両方を提言する材料・構造が求められてきました。

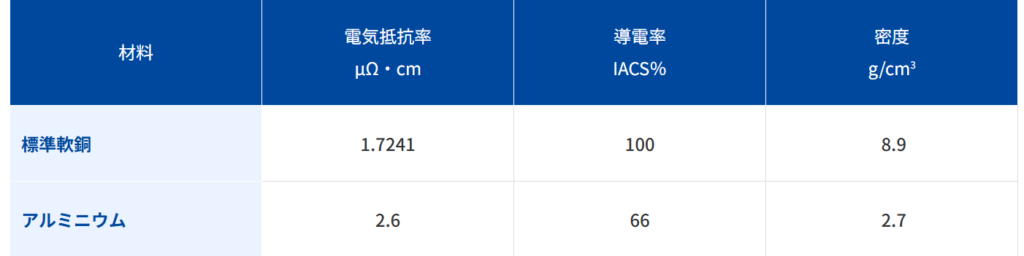

Cu配線の採用:抵抗の低減

従来のAl配線に代わり、より低抵抗率なCuが導入されました。

CuはAlに比べ、約1.5倍の導電性を有しており、同一寸法の配線でより多くの電流を流すことができます。

Low-k材料の採用:静電容量の低減

絶縁膜の静電容量(C)は、次の式で表されます。

C = εA / d

C:静電容量

ε:誘電率(dielectric constant)

A:電極の面積

d:電極間の距離(絶縁膜の厚み)

この式からわかるように、絶縁膜が薄い(dが小さい)ほど、Cは大きくなります。

繰り返しになりますが、静電容量とは、電極間の電気的な影響の受けやすさを示す指標であり、電気が流れないはずの絶縁体を介して、電極内部の電子が偏ってしまう現象です。

つまり電極同士が向き合う距離が近く、絶縁膜が柔らかく反応しやすければ(誘電率が高ければ)、電気的な結びつきが強くなってしまいます。これは、絶縁膜が「電気を通さない壁」ではなく、例えば自動車が走る風圧でたわむガードレールのように、電子の動き(電界)に対して反応してしまうイメージです。

一方で、理想的な絶縁膜は、硬くて頑丈な金属ガードレールのように、電界に対して影響を受けない構造です。

このたわみ=誘電分極(以前の記事:誘電分極)の影響が大きくなると、回路内での信号の切替が遅れたり、隣の配線にまで影響(クロストーク)を及ぼすことになります。

そのため、絶縁膜には、距離を確保しつつ電気的に影響を受けにくい素材が求められます。これを実現するのが、誘電率の低いLow-k材料です。

Low-k材料では、以下のような誘電率低減の工夫が施されています。

- 化学的置換:SiO₂中の酸素をフッ素などに置き換え、原子密度を下げる(例:フッ化SiO₂)

- 多孔質構造(ポーラス):微細な空隙を導入し、誘電率を低減

- 有機系材料:炭素を主成分としたポリマー系絶縁膜など

これらの技術によって低誘電率層間絶縁膜を実現し、配線遅延の大幅な改善が可能となりました。

参照:

SCREEN Cu 配線(https://www.screen.co.jp/spe/technical/guide/cu)

日本半導体歴史館 Low-k材料(https://www.shmj.or.jp/museum2010/exhibi2459.html)

エレクトロマイグレーションの観点から

CuはAlよりもEM耐性は優れていますが、Cu原子の拡散性が高いため、対策が必要です。

なおCuは化学的に酸化されやすい金属でもあり、空気中に放置すると容易に酸化膜が形成されます。そこで、特にCu露出層では、酸化を抑制し信頼性を高めるために、SiCNやCoWPなどのキャップ層が設けられることがあります。

問題と対策

Cu原子が配線から抜けだし絶縁膜(Low-k材料)に入り込むと、絶縁膜がショートしてしまったり、抵抗が増加します。

そこで、

- バリア層による物理的防止:Ta/TaNバリア層で物理的にCu拡散を防止、

- コバルト(Co)、ルテニウム(Ru)など新材料を用いて、バリア構造の追加を不要にし、、

- 構造的工夫として、トレンチ幅の最適化など。

そのうえLow-k材料との界面でCuが浸透/拡散するリスクもあるため、バリア層の設計も重要です。

配線形成方式のちがい

微細配線形式には、大きく分けて2つの方式があります。

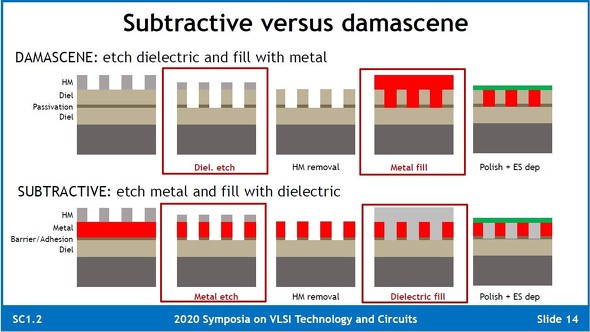

サブトラクティブ方式(Subtractive method)

従来のAl配線で用いられた方式です。

金属膜を全面に成膜したあと、レジストで配線パターンを形成し、不要な部分をエッチングで除去し配線を得ます。

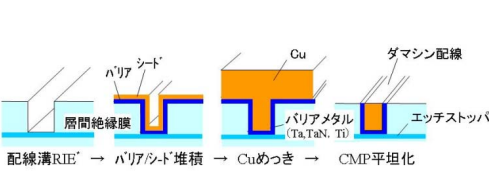

ダマシン方式(Damascene method)

Cu配線に用いられる方式です。

Cuは酸化物は、プラズマエッチングにおいても揮発性の反応生成物を形成しにくいため、従来のAl配線で主流だったドライエッチングで除去するのが困難です。そのため、あらかじめ絶縁膜に配線溝(トレンチ)やビアを形成し、そこへCuを埋め込む「ダマシン方式」が採用されます。

Cu配線におけるダマシン方式の工程

1.絶縁膜への溝形成(トレンチ)

フォトリソグラフィとエッチングにより、絶縁膜(例:Low-k)に配線溝(trench)やビア(via)を形成します。

2.バリア層の成膜

Cuの絶縁膜への拡散を防ぐため、TaやTaNなどのバリア層を成膜します。

3.シード層の成膜

電解メッキを均一に行うための導電層として、スパッタ法により薄いCuシード層を形成します。バリア層の上には直接メッキができないため、このシード層が必要です。

4.Cuの電解メッキによる埋め込み

電解液中でCuイオンを還元し、配線溝・ビア内にCuを析出させます。

※補足:電解メッキとは

導電性の基板(ここではシード層)をカソードとして用い、溶液中の金属イオン(Cu²⁺)を還元して金属膜を析出させる技術です。Cu配線では、高アスペクト比の溝やビアにも高密度かつ均一に金属を充填できるため、従来のPVDでは困難だった微細構造への成膜が可能になります。

5.CMP(化学機械研磨)

余剰なCuを除去し、溝内にのみCu配線を残して表面を平坦化します。

デュアルダマシン構造とは

絶縁膜上の配線の溝とビアホール(下層配線と上層配線とを接続するための開口)とトレンチ(上層配線)を形成し、これらを同時に埋め込み、CMP(砥粒を含むスラリーを供給しながらウエハ表面をパッドにより研磨する工程)によって、溝内にのみ金属を残すことで多層配線を形成することを、デユアルダマシン(dual damascene)といいます。

この方式の利点は、 多層化が容易であること、成膜と平坦化(planarization)の一体化により工程が短縮できること、コスト面でもメリットがあります。

なおシングルダマシン(single damascene)では、ビアと配線を別工程で形成します。各プロセスの融通はききますが、工程数は多くなります。

出典:

『はじめての半導体プロセス』(前田和夫著・技術評論社)

コメント